### Steady-state scheduling on CELL

Mathias Jacquelin,

joint work with Matthieu Gallet, Loris Marchal and Yves Robert

INRIA GRAAL project-team LIP (ENS-Lyon, CNRS, INRIA) École Normale Supérieure de Lyon, France

"Scheduling for large-scale systems" workshop, Knoxville, May 14, 2009.

### <u>Outline</u>

Introduction Steady-state scheduling CELL

Platform and Application Modeling

Mapping the Application

Practical Steady-State on CELL Preprocessing of the schedule State machine of the application Preliminary results

Conclusion and Future works

## **Motivation**

- Multicore architectures: new opportunity to test the scheduling strategies designed in the GRAAL team.

- Our trademark: efficient scheduling on heterogeneous platforms

- Most multicore architecture are homogeneous, regular

Need for tailored algorithms (linear algebra,...)

- Emerging heterogeneous multicore:

- Dedicated processing units on GPUs

- Mixed system: processor + accelerator

- This study: steady-state scheduling on CELL (bounded heterogeneity) to demonstrate the usefulness of complex (static) scheduling techniques

- Ongoing work: only preliminary results

## **Motivation**

- Multicore architectures: new opportunity to test the scheduling strategies designed in the GRAAL team.

- Our trademark: efficient scheduling on heterogeneous platforms

- Most multicore architecture are homogeneous, regular

- Need for tailored algorithms (linear algebra,...)

- Emerging heterogeneous multicore:

- Dedicated processing units on GPUs

- Mixed system: processor + accelerator

- This study: steady-state scheduling on CELL (bounded heterogeneity) to demonstrate the usefulness of complex (static) scheduling techniques

- Ongoing work: only preliminary results

## **Motivation**

- Multicore architectures: new opportunity to test the scheduling strategies designed in the GRAAL team.

- Our trademark: efficient scheduling on heterogeneous platforms

- Most multicore architecture are homogeneous, regular

- Need for tailored algorithms (linear algebra,...)

- Emerging heterogeneous multicore:

- Dedicated processing units on GPUs

- Mixed system: processor + accelerator

- This study: steady-state scheduling on CELL (bounded heterogeneity) to demonstrate the usefulness of complex (static) scheduling techniques

- Ongoing work: only preliminary results

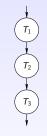

- A pipelined application:

- Simple chain

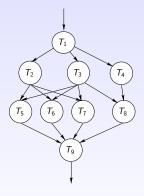

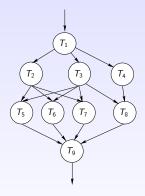

- More complex application (Directed Acyclic Graph)

- Objective: optimize the throughput of the application (number of input files treated per seconds)

- Today: simple case where each task has to be mapped on one single resource

- A pipelined application:

- Simple chain

- More complex application (Directed Acyclic Graph)

- Objective: optimize the throughput of the application (number of input files treated per seconds)

- Today: simple case where each task has to be mapped on one single resource

- A pipelined application:

- Simple chain

- More complex application (Directed Acyclic Graph)

- Objective: optimize the throughput of the application (number of input files treated per seconds)

- Today: simple case where each task has to be mapped on one single resource

- A pipelined application:

- Simple chain

- More complex application (Directed Acyclic Graph)

- Objective: optimize the throughput of the application (number of input files treated per seconds)

- Today: simple case where each task has to be mapped on one single resource

- A pipelined application:

- Simple chain

- More complex application (Directed Acyclic Graph)

- Objective: optimize the throughput of the application (number of input files treated per seconds)

- Today: simple case where each task has to be mapped on one single resource

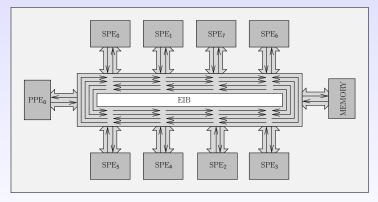

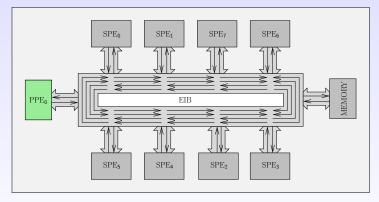

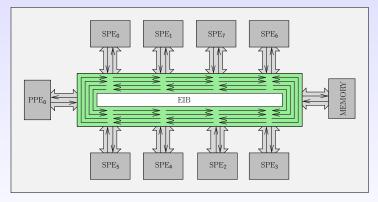

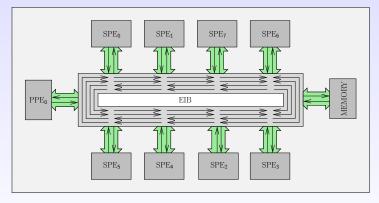

- Multicore heterogeneous processor

- Accelerator extension to Power architecture

- Multicore heterogeneous processor

- Accelerator extension to Power architecture

- Multicore heterogeneous processor

- Accelerator extension to Power architecture

#### ▶ 1 PPE core

- VMX unit

- L1, L2 cache

- 2 way SMT

- Multicore heterogeneous processor

- Accelerator extension to Power architecture

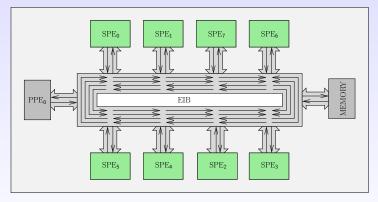

#### 8 SPEs

- 128-bit SIMD instruction set

- Local store 256KB

- Dedicated Asynchronous DMA engine

- Multicore heterogeneous processor

- Accelerator extension to Power architecture

- Multicore heterogeneous processor

- Accelerator extension to Power architecture

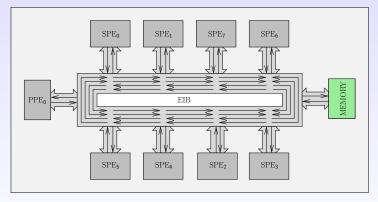

- Element Interconnect Bus (EIB)

- ▶ 200 GB/s bandwidth

- Multicore heterogeneous processor

- Accelerator extension to Power architecture

► 25 GB/s bandwidth

### **Outline**

#### Introduction Steady-state scheduling CELL

#### Platform and Application Modeling

#### Mapping the Application

Practical Steady-State on CELL Preprocessing of the schedule State machine of the application Preliminary results

Conclusion and Future works

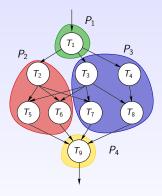

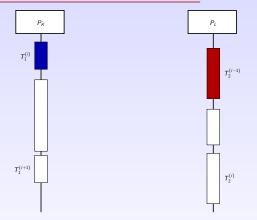

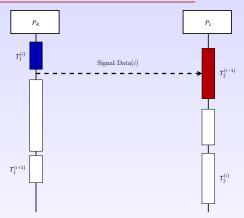

# Platform modeling

Simple CELL modeling:

- 1 PPE and 8 SPE: 9 processing elements P<sub>1</sub>,..., P<sub>9</sub>, with unrelated speed,

- Each processing element access the communication bus with a (bidirectional) bandwidth b = (25GB/s),

- The bus is able to route all concurrent communications without contention (in a first step),

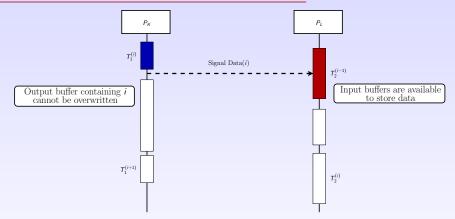

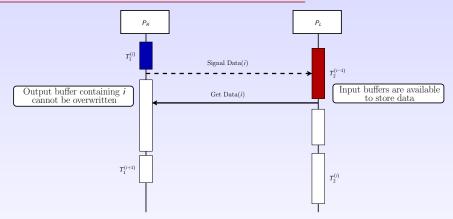

- Due to the limited size of the DMA stack on each SPE:

- Each SPE can perform at most 16 simultaneous DMA operations,

- The PPE can perform at most 8 simultaneous DMA operations to/from a given SPE.

- Linear cost communication model:

a data of size S is sent/received in time S/b

# **Application modeling**

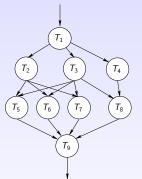

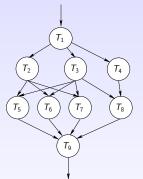

Application is described by a directed acyclic graph:

- Tasks  $T_1, \ldots, T_n$

- Processing time of task T<sub>k</sub> on P<sub>i</sub> is t<sub>i</sub>(k),

- ▶ If there is a dependency  $T_k \rightarrow T_I$ , data<sub>k,l</sub> is the size of the file produced by  $T_k$  and needed by  $T_I$ ,

- If  $T_k$  is an input task, it reads read<sub>k</sub> bytes from main memory,

- If  $T_k$  is an output task, it writes write bytes to main memory,

# **Application modeling**

Application is described by a directed acyclic graph:

- Tasks  $T_1, \ldots, T_n$

- Processing time of task T<sub>k</sub> on P<sub>i</sub> is t<sub>i</sub>(k),

- If there is a dependency T<sub>k</sub> → T<sub>l</sub>, data<sub>k,l</sub> is the size of the file produced by T<sub>k</sub> and needed by T<sub>l</sub>,

If T<sub>k</sub> is an input task, it reads read<sub>k</sub> bytes from main memory,

If T<sub>k</sub> is an output task, it writes write<sub>k</sub> bytes to main memory,

# **Application modeling**

Application is described by a directed acyclic graph:

- Tasks  $T_1, \ldots, T_n$

- Processing time of task T<sub>k</sub> on P<sub>i</sub> is t<sub>i</sub>(k),

- If there is a dependency T<sub>k</sub> → T<sub>l</sub>, data<sub>k,l</sub> is the size of the file produced by T<sub>k</sub> and needed by T<sub>l</sub>,

- If  $T_k$  is an input task, it reads read k bytes from main memory,

- If  $T_k$  is an output task, it writes write<sub>k</sub> bytes to main memory,

# Target application: vocoder

### **Outline**

Introduction Steady-state scheduling CELL

Platform and Application Modeling

#### Mapping the Application

Practical Steady-State on CELL Preprocessing of the schedule State machine of the application Preliminary results

Conclusion and Future works

- Ojective: maximize throughput  $\rho$

- Method: write a linear program gathering constraints on the mapping

► Binary variables:

$$\alpha_i^k = \begin{cases} 1 & \text{if } T_k \text{ is mapped on } P_i \\ 0 & \text{otherwise} \end{cases}$$

► Other useful binary variables: β<sup>k,l</sup><sub>i,j</sub> = 1 iff file T<sub>k</sub> → T<sub>l</sub> is transfered from P<sub>i</sub> to P<sub>j</sub>

# **Constraints** 1/2

On the application structure:

Each task is mapped on a processor:

$$\forall T_k \quad \sum_i \alpha_i^k = 1$$

► Given a dependency T<sub>k</sub> → T<sub>l</sub>, the processor computing T<sub>l</sub> must receive the corresponding file:

$$\forall (k, l) \in E, \forall P_j, \quad \sum_i \beta_{i,j}^{k,l} \ge \alpha_j^l$$

• Given a dependency  $T_k \rightarrow T_l$ , only the processor computing  $T_k$  can send the corresponding file:

$$\forall (k, l) \in E, \forall P_i, \quad \sum_j \beta_{i,j}^{k,l} \leq \alpha_i^k$$

# **Constraints 2/2**

On the achievable throughput  $\rho=1/\,{\cal T}$  :

• On a given processor, all tasks must be completed within T:

$$\forall P_i, \quad \sum_k \alpha_i^k \times t_i(k) \leq T$$

All incoming communications must be completed within T:

$$\forall P_j, \quad \frac{1}{b} \Big( \sum_k \alpha_j^k \times \mathsf{read}_k + \sum_{k,l} \sum_i \beta_{i,j}^{k,l} \times \mathsf{data}_{k,l} \Big) \leq T$$

► All outgoing communications must be completed within *T*:

$$\forall \mathsf{P}_i, \quad \frac{1}{b} \Big( \sum_k \alpha_i^k \times \mathsf{write}_k + \sum_{k,l} \sum_i \beta_{i,j}^{k,l} \times \mathsf{data}_{k,l} \Big) \leq \mathsf{T}$$

- + constraints on the number of incoming/outgoing communications to respect the DMA requirements

- + constraints on the available memory on SPE

# **Optimal mapping computation**

- $\blacktriangleright$  Linear program with the objective of minimizing  ${\cal T}$

- Integer (binary) variables: Mixed Integer Programming

- NP-complete problem

- Efficient solvers exist with short running time

- for small-size problems

- or when an approximate solution is searched

- We use CPLEX, and look for an approximate solution (5% of the optimal throughput is good enough)

### **Outline**

Introduction Steady-state scheduling CELL

Platform and Application Modeling

Mapping the Application

#### Practical Steady-State on CELL

Preprocessing of the schedule State machine of the application Preliminary results

Conclusion and Future works

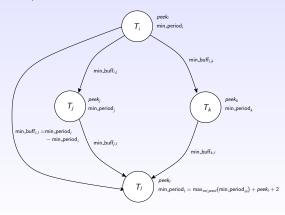

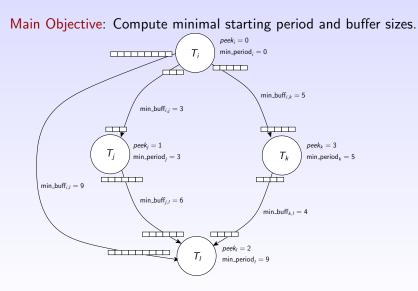

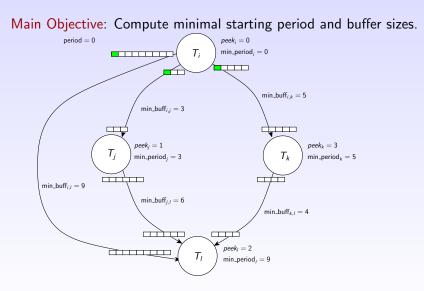

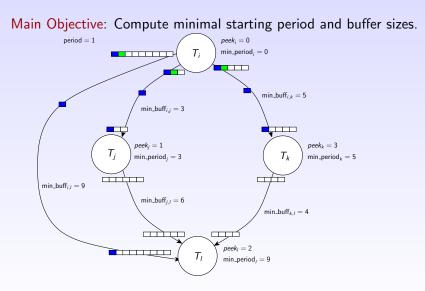

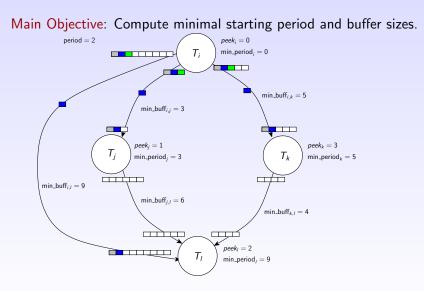

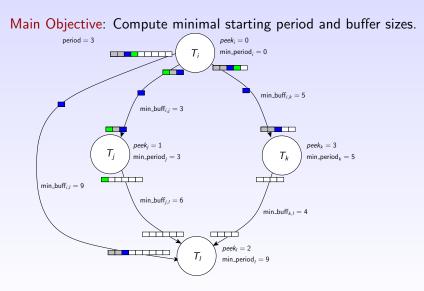

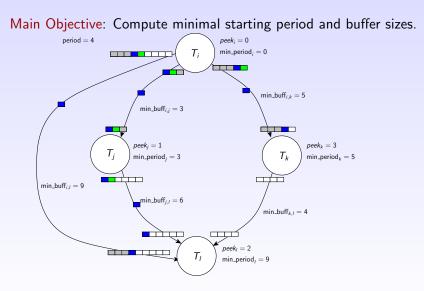

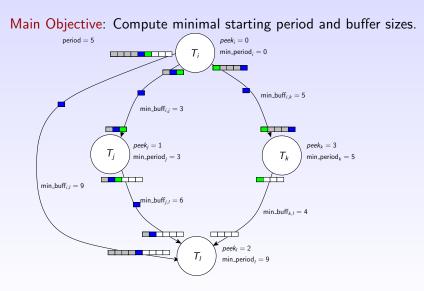

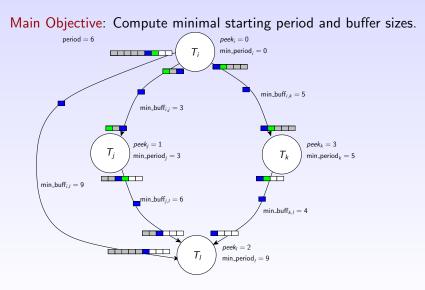

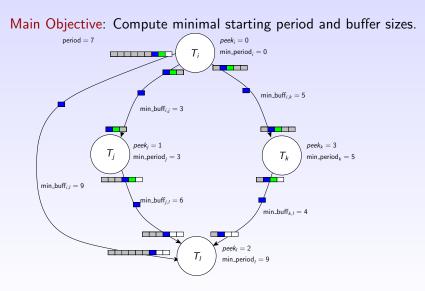

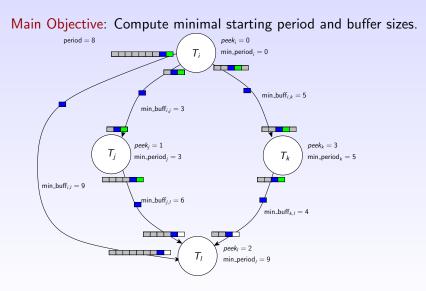

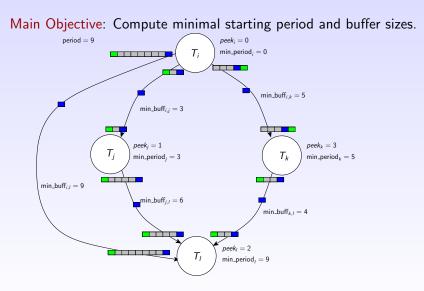

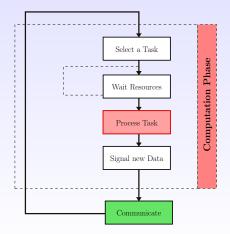

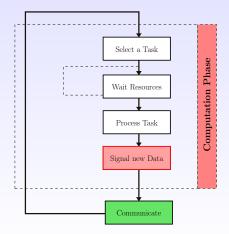

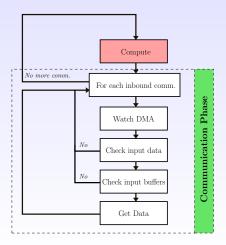

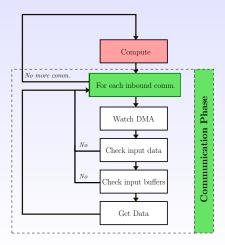

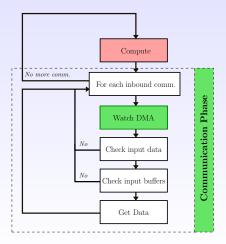

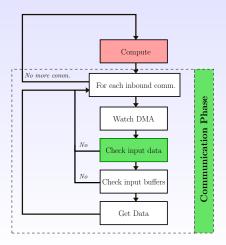

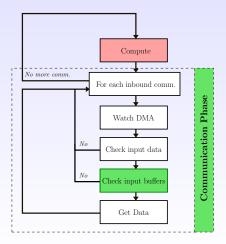

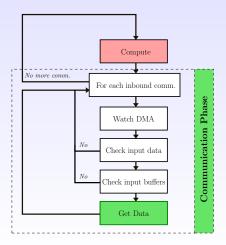

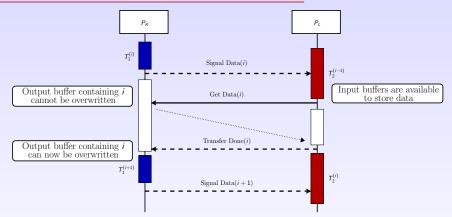

Main Objective: Compute minimal starting period and buffer sizes.

- $\min_{period_l} = \max_{m \in precl} (\min_{period_m}) + peek_l + 2$

- $\min_{i,l} = \min_{i,l} \min_$

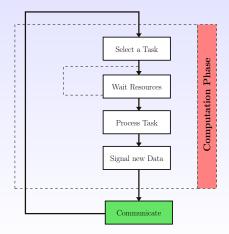

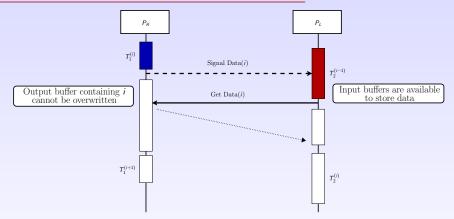

mfc\_putb for SPEs' outbound communications.

spe\_mfcio\_getb for PPEs' outbound communications to SPEs.

memcpy for PPEs' outbound communications to main memory.

mfc\_putb for SPEs' outbound communications.

spe\_mfcio\_getb for PPEs' outbound communications to SPEs.

memcpy for PPEs' outbound communications to main memory.

mfc\_get for SPEs' inbound communications.

spe\_mfcio\_put for PPEs' inbound communications from SPEs.

memcpy for PPEs' inbound communications from main memory.

mfc\_get for SPEs' inbound communications.

spe\_mfcio\_put for PPEs' inbound communications from SPEs.

memcpy for PPEs' inbound communications from main memory.

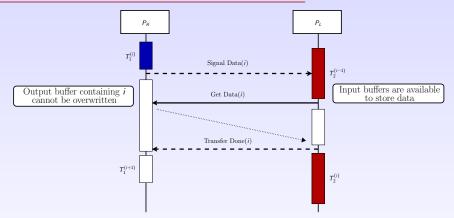

mfc\_putb for SPEs' acknowledgements.

spe\_mfcio\_getb for PPEs' acknowledgements to SPEs.

Self acknowledgement of PPEs' transfers from main memory.

mfc\_putb for SPEs' acknowledgements.

spe\_mfcio\_getb for PPEs' acknowledgements to SPEs.

Self acknowledgement of PPEs' transfers from main memory.

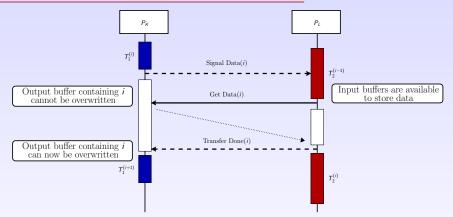

mfc\_putb for SPEs' acknowledgements.

spe\_mfcio\_getb for PPEs' acknowledgements to SPEs.

Self acknowledgement of PPEs' transfers from main memory.

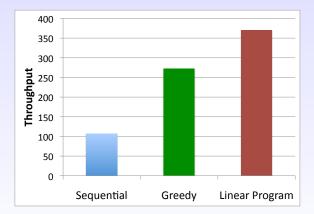

## **Preliminary results**

We outperform both greedy heuristic and sequential version.

Results are obtained over 70000 periods

#### **Outline**

Introduction Steady-state scheduling CELL

Platform and Application Modeling

Mapping the Application

Practical Steady-State on CELL Preprocessing of the schedule State machine of the application Preliminary results

Conclusion and Future works

# Feedback on Cell programming

Multilevel heterogeneity:

- ► 32 bits SPEs vs 64 bits PPE architectures

- Different communication mechanism and constraints

- Non trivial initialization phase

- Varying data structure sizes (32/64bits)

- Runtime memory allocation

# **On-going and Future work**

- Various code optimizations

- SIMD code for SPEs

- Reduce control overhead

- Better communication modeling

- Is linear cost model relevant ?

- Contention on concurrent DMA operations ?

- Larger platforms

- Using multiple CELL processors

- CELL + other type of processing units ?

- Work on communication modeling

- Design scheduling heuristics

- MIP is costly