# Complexity analysis of matrix product on multicore architectures

Mathias Jacquelin, Loris Marchal and Yves Robert

Ecole Normale Supérieure de Lyon Mathias.Jacquelin@ens-lyon.fr http://graal.ens-lyon.fr/~mjacquel

Rocquencourt, February 4, 2009

Complexity

From simple single core architectures . . .

### Recent evolution of processors

From simple single core architectures . . .

Speed used to be obtained through ILP

... to multi-core and upcoming many-core processors

... to multi-core and upcoming many-core processors

Now, algorithms need to explicitly exploit TLP, similar to classical parallel programming

... to multi-core and upcoming many-core processors

Now, algorithms need to explicitly exploit TLP, similar to classical parallel programming

More important: must efficiently use memory, especially caches

Target algorithms: Dense linear algebra kernels (key to performance for many scientific applications)

Calls for revisiting old problems

- Algorithms based on a 2D grid topology are not well suited for multicore architectures

- Hierarchy of cache memories

- Need to take further advantage of data locality

Target algorithms: Dense linear algebra kernels (key to performance for many scientific applications)

#### Calls for revisiting old problems

- Algorithms based on a 2D grid topology are not well suited for multicore architectures

- Hierarchy of cache memories

- Need to take further advantage of data locality

Target algorithms: Dense linear algebra kernels (key to performance for many scientific applications)

#### Calls for revisiting old problems

- Algorithms based on a 2D grid topology are not well suited for multicore architectures

- Hierarchy of cache memories

- Need to take further advantage of data locality

Target algorithms: Dense linear algebra kernels (key to performance for many scientific applications)

#### Calls for revisiting old problems

- Algorithms based on a 2D grid topology are not well suited for multicore architectures

- Hierarchy of cache memories

- Need to take further advantage of data locality

Target algorithms: Dense linear algebra kernels (key to performance for many scientific applications)

#### Calls for revisiting old problems

- Algorithms based on a 2D grid topology are not well suited for multicore architectures

- Hierarchy of cache memories

- Need to take further advantage of data locality

- Problem statement

- Modeling multicore architectures

- Studied case and objectives

Problem statement

- Lower bound on communication

- Maximum re-use algorithm for multicore architectures

- Minimizing the number of shared-cache misses

- Minimizing the number of distributed-cache misses

- Minimizing data access time

- Experimental results

- Conclusion

Complexity

- Problem statement

- Modeling multicore architectures

- Studied case and objectives

- Lower bound on communication

- 2 Maximum re-use algorithm for multicore architectures

- Minimizing the number of shared-cache misses

- Minimizing the number of distributed-cache misses

- Minimizing data access time

- Experimental results

- 3 Conclusion

- Problem statement

- Modeling multicore architectures

- Studied case and objectives

- Lower bound on communication

- Maximum re-use algorithm for multicore architectures

- Minimizing the number of shared-cache misses

- Minimizing the number of distributed-cache misses

- Minimizing data access time

- Experimental results

- 3 Conclusion

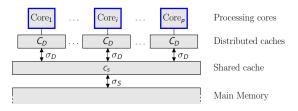

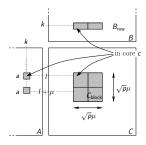

#### Difficulty: Come up with a realistic but still tractable model

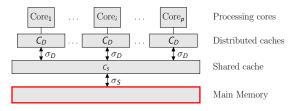

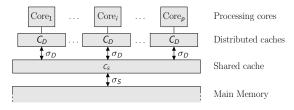

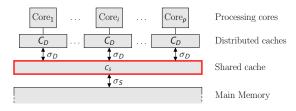

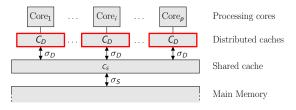

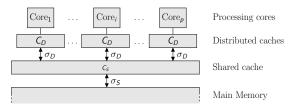

- p identical cores, computing speed w

Complexity

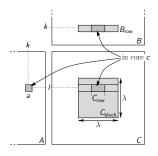

- p identical cores, computing speed w

- Large main memory

- p identical cores, computing speed w

- Large main memory

- Two levels of caches:

- a first level shared by all cores of size  $C_S$  and bandwidth  $\sigma_S$

- a second level of cache distributed, each of size  $C_D$  and bandwidth  $\sigma_D$

- Caches are inclusive and fully associative

- p identical cores, computing speed w

- Large main memory

- Two levels of caches:

- ullet a first level shared by all cores of size  $\mathcal{C}_S$  and bandwidth  $\sigma_S$

- a second level of cache distributed, each of size  $C_D$  and bandwidth  $\sigma_D$

- Caches are inclusive and fully associative

- p identical cores, computing speed w

- Large main memory

- Two levels of caches:

- a first level shared by all cores of size  $C_S$  and bandwidth  $\sigma_S$

- a second level of cache distributed, each of size  $C_D$  and bandwidth  $\sigma_D$

- Caches are inclusive and fully associative

- p identical cores, computing speed w

- Large main memory

- Two levels of caches:

- ullet a first level shared by all cores of size  $\mathcal{C}_{\mathcal{S}}$  and bandwidth  $\sigma_{\mathcal{S}}$

- a second level of cache distributed, each of size  $C_D$  and bandwidth  $\sigma_D$

- Caches are inclusive and fully associative

- Problem statement

- Modeling multicore architectures

- Studied case and objectives

- Lower bound on communication

- Maximum re-use algorithm for multicore architectures

- Minimizing the number of shared-cache misses

- Minimizing the number of distributed-cache misses

- Minimizing data access time

- Experimental results

- Conclusion

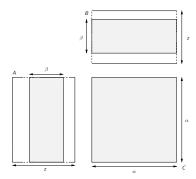

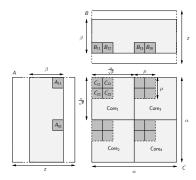

Target: Compute the matrix product  $C = A \times B$ .

• A is  $m \times z$ , B is  $z \times n$  and C has size  $m \times n$

We use a block-oriented approach, thus, manipulate square blocks of coefficients.

First objective: Communication volume of shared cache.

$\bullet$   $M_S$  is the number of cache misses in the shared cache

Second objective: Communication volume of distributed caches.

$\bullet$   $M_D$  is the maximum of all distributed caches misses

Third objective: Overall time  $T_{data}$  required for data movement.

•

$$T_{\text{data}} = \frac{M_S}{\sigma_S} + \frac{M_D}{\sigma_D}$$

Target: Compute the matrix product  $C = A \times B$ .

• A is  $m \times z$ , B is  $z \times n$  and C has size  $m \times n$

We use a block-oriented approach, thus, manipulate square blocks of coefficients.

First objective: Communication volume of shared cache.

ullet  $M_S$  is the number of cache misses in the shared cache

Second objective: Communication volume of distributed caches.

$\bullet$   $M_D$  is the maximum of all distributed caches misses

Third objective: Overall time  $T_{data}$  required for data movement.

•

$$T_{\text{data}} = \frac{M_S}{\sigma_S} + \frac{M_D}{\sigma_D}$$

Target: Compute the matrix product  $C = A \times B$ .

• A is  $m \times z$ , B is  $z \times n$  and C has size  $m \times n$

We use a block-oriented approach, thus, manipulate square blocks of coefficients.

First objective: Communication volume of shared cache.

• *M<sub>S</sub>* is the number of cache misses in the shared cache

Second objective: Communication volume of distributed caches.

ullet  $M_D$  is the maximum of all distributed caches misses

Third objective: Overall time  $T_{data}$  required for data movement.

•

$$T_{\text{data}} = \frac{M_S}{\sigma_S} + \frac{M_D}{\sigma_D}$$

Target: Compute the matrix product  $C = A \times B$ .

• A is  $m \times z$ , B is  $z \times n$  and C has size  $m \times n$

We use a block-oriented approach, thus, manipulate square blocks of coefficients.

First objective: Communication volume of shared cache.

$\bullet$   $M_S$  is the number of cache misses in the shared cache

Second objective: Communication volume of distributed caches.

ullet  $M_D$  is the maximum of all distributed caches misses

Third objective: Overall time  $T_{data}$  required for data movement.

•

$$T_{\text{data}} = \frac{M_S}{\sigma_S} + \frac{M_D}{\sigma_D}$$

- Problem statement

- Modeling multicore architectures

- Studied case and objectives

- Lower bound on communication

- Maximum re-use algorithm for multicore architectures

- Minimizing the number of shared-cache misses

- Minimizing the number of distributed-cache misses

- Minimizing data access time

- Experimental results

- 3 Conclusion

#### Lower bound on communication

- Irony, Toledo and Tiskin show that on a system with a memory of size M, the communication-to-computation ratio of matrix product is lower-bounded by:  $\sqrt{\frac{27}{8M}}$ .

- In our case, with comp(c) being the amount of computation done by core c, we have:

- $CCR_S = M_S/(\sum_c comp(c))$  for the shared cache

- $CCR_D = \frac{1}{p} \sum_{c=1}^{p} (M_D/comp(c))$  for the distributed cache.

- In all our algorithms, the amount of computation is equally balanced among cores, so that comp(c) = mnz/p for all cores. Therefore:

$$CCR_S \ge \sqrt{\frac{27}{8C_S}}$$

and  $CCR_D \ge \sqrt{\frac{27}{8C_D}}$ .

- Problem statement

- Modeling multicore architectures

- Studied case and objectives

- Lower bound on communication

- 2 Maximum re-use algorithm for multicore architectures

- Minimizing the number of shared-cache misses

- Minimizing the number of distributed-cache misses

- Minimizing data access time

- Experimental results

- Conclusion

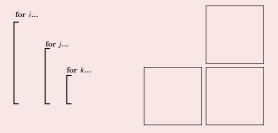

Main Objective: Create a data-thrifty algorithm, memory of size M

Rule 1 Loaded data must be re-used as much as possible

Main Objective: Create a data-thrifty algorithm, memory of size M

Rule 1 Loaded data must be re-used as much as possible Rule 2 In a given loop, required data must be loaded once

### Main Objective: Create a data-thrifty algorithm, memory of size M

Rule 1 Loaded data must be re-used as much as possible Rule 2 In a given loop, required data must be loaded once

### Main Objective: Create a data-thrifty algorithm, memory of size M

Rule 1 Loaded data must be re-used as much as possible Rule 2 In a given loop, required data must be loaded once

Problem statement

#### Main Objective: Create a data-thrifty algorithm, memory of size M

Rule 1 Loaded data must be re-used as much as possible Rule 2 In a given loop, required data must be loaded once

Observation Outermost loop is prevalent in order to minimize loaded data

#### Main Objective: Create a data-thrifty algorithm, memory of size M

Rule 1 Loaded data must be re-used as much as possible Rule 2 In a given loop, required data must be loaded once

Corollary 1 In outermost loop, load the largest square blocks

Problem statement

#### Main Objective: Create a data-thrifty algorithm, memory of size M

Rule 1 Loaded data must be re-used as much as possible Rule 2 In a given loop, required data must be loaded once

Corollary 1 In outermost loop, load the largest square blocks

#### Main Objective: Create a data-thrifty algorithm, memory of size M

Rule 1 Loaded data must be re-used as much as possible Rule 2 In a given loop, required data must be loaded once

Corollary 1 In outermost loop, load the largest square blocks Corollary 2 In inner loops, load the smallest block allowing to respect Rules 1 & 2.

### Main Objective: Create a data-thrifty algorithm, memory of size M

Rule 1 Loaded data must be re-used as much as possible Rule 2 In a given loop, required data must be loaded once

Corollary 1 In outermost loop, load the largest square blocks Corollary 2 In inner loops, load the smallest block allowing to respect Rules 1 & 2.

Problem statement

### Main Objective: Create a data-thrifty algorithm, memory of size M

Rule 1 Loaded data must be re-used as much as possible Rule 2 In a given loop, required data must be loaded once

Corollary 1 In outermost loop, load the largest square blocks Corollary 2 In inner loops, load the smallest block allowing to respect Rules 1 & 2.

Problem statement

### Main Objective: Create a data-thrifty algorithm, memory of size M

- Rule 1 Loaded data must be re-used as much as possible

- Rule 2 In a given loop, required data must be loaded once

- Corollary 1 In outermost loop, load the largest square blocks

- Corollary 2 In inner loops, load the smallest block allowing to respect Rules 1 & 2.

#### How?

• Split the available memory into  $1 + \alpha + \alpha^2$  blocks

### Main Objective: Create a data-thrifty algorithm, memory of size M

- Rule 1 Loaded data must be re-used as much as possible

- Rule 2 In a given loop, required data must be loaded once

- Corollary 1 In outermost loop, load the largest square blocks

- Corollary 2 In inner loops, load the smallest block allowing to respect Rules 1 & 2.

#### How?

• Split the available memory into  $1 + \alpha + \alpha^2$  blocks

#### Result

• A CCR of  $\frac{2}{\sqrt{M}}$  for a memory of size M for large matrices

- Must take into account both cache levels:

- Previous data allocation scheme adapted so as to fit caches.

- Must take into account both cache levels:

- Previous data allocation scheme adapted so as to fit caches.

- Must take into account both cache levels:

- Previous data allocation scheme adapted so as to fit caches.

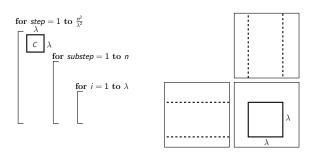

- Two parameters depending on cache sizes:

- $\lambda$  is the largest integer with  $1 + \lambda + \lambda^2 \leq C_S$

- $\mu$  is the largest integer with  $1 + \mu + \mu^2 \leq C_D$

- These parameters will be used separately

- ullet For the sake of simplicity, we assume that  $\lambda$  is a multiple of  $\mu$

- Must take into account both cache levels:

- Previous data allocation scheme adapted so as to fit caches.

- Two parameters depending on cache sizes:

- $\lambda$  is the largest integer with  $1 + \lambda + \lambda^2 \leq C_S$

- $\mu$  is the largest integer with  $1 + \mu + \mu^2 \leq C_D$

- These parameters will be used separately

- ullet For the sake of simplicity, we assume that  $\lambda$  is a multiple of  $\mu$

- Must take into account both cache levels:

- Previous data allocation scheme adapted so as to fit caches.

- Two parameters depending on cache sizes:

- $\lambda$  is the largest integer with  $1 + \lambda + \lambda^2 \leq C_S$

- $\mu$  is the largest integer with  $1 + \mu + \mu^2 \leq C_D$

- These parameters will be used separately

- ullet For the sake of simplicity, we assume that  $\lambda$  is a multiple of  $\mu$

- Must take into account both cache levels:

- Previous data allocation scheme adapted so as to fit caches.

- Two parameters depending on cache sizes:

- $\lambda$  is the largest integer with  $1 + \lambda + \lambda^2 \leq C_S$

- $\mu$  is the largest integer with  $1 + \mu + \mu^2 \leq C_D$

- These parameters will be used separately

- ullet For the sake of simplicity, we assume that  $\lambda$  is a multiple of  $\mu$

- Must take into account both cache levels:

- Previous data allocation scheme adapted so as to fit caches.

- Two parameters depending on cache sizes:

- $\lambda$  is the largest integer with  $1 + \lambda + \lambda^2 \leq C_S$

- $\mu$  is the largest integer with  $1 + \mu + \mu^2 \leq C_D$

- These parameters will be used separately

- $\bullet$  For the sake of simplicity, we assume that  $\lambda$  is a multiple of  $\mu$

### Outline

- Problem statement

- Modeling multicore architectures

- Studied case and objectives

- Lower bound on communication

- 2 Maximum re-use algorithm for multicore architectures

- Minimizing the number of shared-cache misses

- Minimizing the number of distributed-cache misses

- Minimizing data access time

- Experimental results

- 3 Conclusion

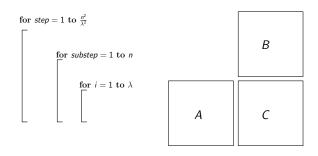

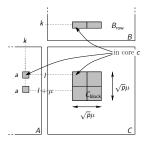

#### • We load in shared cache:

- A square block of size  $\lambda^2$  of C

- A row of  $\lambda$  elements of B

- One element of A

- Then, rows of  $C_{block}$  and elements of A are distributed and

- Repeat until the block of C had been fully updated.

- We load in shared cache:

- A square block of size  $\lambda^2$  of C

- A row of  $\lambda$  elements of B

- One element of A

- Then, rows of  $C_{\text{block}}$  and elements of A are distributed and computed.

- Repeat until the block of C had been fully updated.

- We load in shared cache:

- A square block of size  $\lambda^2$  of C

- A row of  $\lambda$  elements of B

- One element of A

- Then, rows of  $C_{block}$  and elements of A are distributed and

- We load in shared cache:

- A square block of size  $\lambda^2$  of C

- A row of  $\lambda$  elements of B

- One element of A

- Then, rows of  $C_{block}$  and elements of A are distributed and

• We load in shared cache:

Problem statement

- A square block of size  $\lambda^2$  of C

- A row of  $\lambda$  elements of B

- One element of A

- Then, rows of  $C_{block}$  and elements of A are distributed and

- We load in shared cache:

- A square block of size  $\lambda^2$  of C

- A row of  $\lambda$  elements of B

- One element of A

- $\bullet$  Then, rows of  $C_{block}$  and elements of A are distributed and computed.

- We load in shared cache:

- A square block of size  $\lambda^2$  of C

- A row of  $\lambda$  elements of B

- One element of A

- $\bullet$  Then, rows of  $C_{block}$  and elements of A are distributed and computed.

- We load in shared cache:

- A square block of size  $\lambda^2$  of C

- A row of  $\lambda$  elements of B

- One element of A

- $\bullet$  Then, rows of  $C_{block}$  and elements of A are distributed and computed.

- Repeat until the block of C had been fully updated.

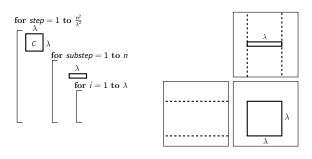

#### Shared-cache misses

- Elements of C are loaded once in shared cache

- For each block of size  $\lambda^2$ . z rows of size  $\lambda$  are loaded from B as well as  $z \times \lambda$  elements of A.

- $M_S = mn + 2mnz/\lambda$

- For large matrices, CCR is  $2/\lambda$   $\odot$

- load z times  $\lambda$  elements of A one by one

- load z rows of size  $\lambda/p$  of B

- update  $\lambda \times z$  times rows of size  $\lambda/p$  of C

•

$$M_D = \frac{mnz}{\lambda} \times (1 + 1/p + \lambda/p)$$

• CCR is  $(p+1)/\lambda + 1 \odot$

#### Shared-cache misses

- Elements of C are loaded once in shared cache

- For each block of size  $\lambda^2$ . z rows of size  $\lambda$  are loaded from B as well as  $z \times \lambda$  elements of A.

- $M_S = mn + 2mnz/\lambda$

- For large matrices, CCR is  $2/\lambda$   $\odot$

- load z times  $\lambda$  elements of A one by one

- load z rows of size  $\lambda/p$  of B

- update  $\lambda \times z$  times rows of size  $\lambda/p$  of C

•

$$M_D = \frac{mnz}{\lambda} \times (1 + 1/p + \lambda/p)$$

• CCR is  $(p+1)/\lambda + 1 \odot$

#### Shared-cache misses

- Elements of C are loaded once in shared cache

- For each block of size  $\lambda^2$ . z rows of size  $\lambda$  are loaded from B as well as  $z \times \lambda$  elements of A.

- $M_S = mn + \frac{2mnz}{\lambda}$

- For large matrices, CCR is  $2/\lambda$   $\odot$

- load z times  $\lambda$  elements of A one by one

- load z rows of size  $\lambda/p$  of B

- update  $\lambda \times z$  times rows of size  $\lambda/p$  of C

•

$$M_D = \frac{mnz}{\lambda} \times (1 + 1/p + \lambda/p)$$

• CCR is  $(p+1)/\lambda + 1 \odot$

#### Shared-cache misses

- Elements of C are loaded once in shared cache

- For each block of size  $\lambda^2$ . z rows of size  $\lambda$  are loaded from B as well as  $z \times \lambda$  elements of A.

- $M_S = mn + 2mnz/\lambda$

- For large matrices, CCR is  $2/\lambda$   $\odot$

- load z times  $\lambda$  elements of A one by one

- load z rows of size  $\lambda/p$  of B

- update  $\lambda \times z$  times rows of size  $\lambda/p$  of C

Complexity

•

$$M_D = \frac{mnz}{\lambda} \times (1 + 1/p + \lambda/p)$$

• CCR is  $(p+1)/\lambda + 1 \odot$

#### Shared-cache misses

- Elements of C are loaded once in shared cache

- For each block of size  $\lambda^2$ . z rows of size  $\lambda$  are loaded from B as well as  $z \times \lambda$  elements of A.

- $M_S = mn + 2mnz/\lambda$

- For large matrices, CCR is  $2/\lambda$   $\odot$

Distributed-cache misses At each step, we:

- load z times  $\lambda$  elements of A one by one

- load z rows of size  $\lambda/p$  of B

- update  $\lambda \times z$  times rows of size  $\lambda/p$  of C

•

$$M_D = \frac{mnz}{\lambda} \times (1 + 1/p + \lambda/p)$$

• CCR is  $(p+1)/\lambda + 1$

#### Shared-cache misses

- Elements of C are loaded once in shared cache

- For each block of size  $\lambda^2$ . z rows of size  $\lambda$  are loaded from B as well as  $z \times \lambda$  elements of A.

- $M_S = mn + 2mnz/\lambda$

- For large matrices, CCR is  $2/\lambda$   $\odot$

Distributed-cache misses At each step, we:

- load z times  $\lambda$  elements of A one by one

- load z rows of size  $\lambda/p$  of B

- update  $\lambda \times z$  times rows of size  $\lambda/p$  of C

•

$$M_D = \frac{mnz}{\lambda} \times (1 + 1/p + \lambda/p)$$

• CCR is  $(p+1)/\lambda + 1$

#### Shared-cache misses

- Elements of C are loaded once in shared cache

- For each block of size  $\lambda^2$ . z rows of size  $\lambda$  are loaded from B as well as  $z \times \lambda$  elements of A.

- $M_S = mn + 2mnz/\lambda$

- For large matrices, CCR is  $2/\lambda$   $\odot$

Distributed-cache misses At each step, we:

- load z times  $\lambda$  elements of A one by one

- load z rows of size  $\lambda/p$  of B

- update  $\lambda \times z$  times rows of size  $\lambda/p$  of C

•

$$M_D = \frac{mnz}{\lambda} \times (1 + 1/p + \lambda/p)$$

• CCR is  $(p+1)/\lambda + 1$

#### Shared-cache misses

- Elements of C are loaded once in shared cache

- For each block of size  $\lambda^2$ , z rows of size  $\lambda$  are loaded from B as well as  $z \times \lambda$  elements of A.

- $M_S = mn + 2mnz/\lambda$

- For large matrices, CCR is  $2/\lambda$   $\odot$

Distributed-cache misses At each step, we:

- load z times  $\lambda$  elements of A one by one

- load z rows of size  $\lambda/p$  of B

- update  $\lambda \times z$  times rows of size  $\lambda/p$  of C

•

$$M_D = \frac{mnz}{\lambda} \times (1 + 1/p + \frac{\lambda/p}{p})$$

• CCR is  $(p+1)/\lambda + 1 \odot$

#### Shared-cache misses

- Elements of C are loaded once in shared cache

- For each block of size  $\lambda^2$ . z rows of size  $\lambda$  are loaded from B as well as  $z \times \lambda$  elements of A.

- $M_S = mn + 2mnz/\lambda$

- For large matrices, CCR is  $2/\lambda$   $\odot$

Distributed-cache misses At each step, we:

- load z times  $\lambda$  elements of A one by one

- load z rows of size  $\lambda/p$  of B

- update  $\lambda \times z$  times rows of size  $\lambda/p$  of C

•

$$M_D = \frac{mnz}{\lambda} \times (1 + 1/p + \lambda/p)$$

• CCR is  $(p+1)/\lambda + 1 \odot$

### Outline

- Problem statement

- Modeling multicore architectures

- Studied case and objectives

- Lower bound on communication

- 2 Maximum re-use algorithm for multicore architectures

- Minimizing the number of shared-cache misses

- Minimizing the number of distributed-cache misses

- Minimizing data access time

- Experimental results

- 3 Conclusion

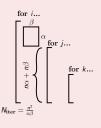

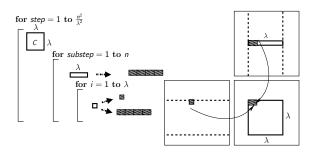

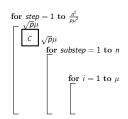

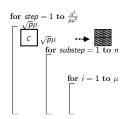

for

$$step = 1$$

to  $\frac{n^2}{p\mu^2}$

for  $substep = 1$  to  $n$

for  $i = 1$  to  $\mu$

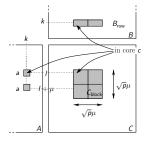

- $\mu$  is the largest integer with  $1 + \mu + \mu^2 \leq C_D$

- A square block of size  $(\sqrt{p}\mu)^2$  of C is loaded in the shared cache and, subblocks of size  $\mu^2$  are distributed to every cores

- Then, repeatedly, z times:

- ullet a row of  $\sqrt{

ho\mu}$  elements of B is loaded in the shared cache and distributed

- $\sqrt{p}$  elements of A are sequentially read  $\mu$  times in shared cache and distributed in order to contribute to current

- $\mu$  is the largest integer with  $1 + \mu + \mu^2 < C_D$

- A square block of size  $(\sqrt{p}\mu)^2$  of C is loaded in the shared cache and, subblocks of size  $\mu^2$  are distributed to every cores

- Then, repeatedly, z times:

19/32

- $\mu$  is the largest integer with  $1 + \mu + \mu^2 < C_D$

- A square block of size  $(\sqrt{p}\mu)^2$  of C is loaded in the shared cache and, subblocks of size  $\mu^2$  are distributed to every cores

- Then, repeatedly, z times:

Introduction

- $\mu$  is the largest integer with  $1 + \mu + \mu^2 \leq C_D$

- A square block of size  $(\sqrt{p}\mu)^2$  of C is loaded in the shared cache and, subblocks of size  $\mu^2$  are distributed to every cores

- Then, repeatedly, z times:

- a row of  $\sqrt{p}\mu$  elements of B is loaded in the shared cache and distributed

- $\sqrt{p}$  elements of A are sequentially read  $\mu$  times in shared cache and distributed in order to contribute to current sub-blocks of C

- $\mu$  is the largest integer with  $1 + \mu + \mu^2 < C_D$

- A square block of size  $(\sqrt{p}\mu)^2$  of C is loaded in the shared cache and, subblocks of size  $\mu^2$  are distributed to every cores

- Then, repeatedly, z times:

- a row of  $\sqrt{p}\mu$  elements of B is loaded in the shared cache and distributed

- $\sqrt{p}$  elements of A are sequentially read  $\mu$  times in shared

- $\mu$  is the largest integer with  $1 + \mu + \mu^2 < C_D$

- A square block of size  $(\sqrt{p}\mu)^2$  of C is loaded in the shared cache and, subblocks of size  $\mu^2$  are distributed to every cores

- Then, repeatedly, z times:

- a row of  $\sqrt{p}\mu$  elements of B is loaded in the shared cache and distributed

- $\sqrt{p}$  elements of A are sequentially read  $\mu$  times in shared

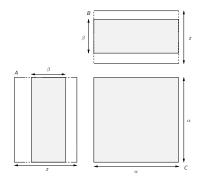

#### Minimizing the number of distributed-cache misses

- $\mu$  is the largest integer with  $1 + \mu + \mu^2 < C_D$

- A square block of size  $(\sqrt{p}\mu)^2$  of C is loaded in the shared cache and, subblocks of size  $\mu^2$  are distributed to every cores

- Then, repeatedly, z times:

- a row of  $\sqrt{p}\mu$  elements of B is loaded in the shared cache and distributed

- $\sqrt{p}$  elements of A are sequentially read  $\mu$  times in shared cache and distributed in order to contribute to current sub-blocks of C

#### Minimizing the number of distributed-cache misses

- $\mu$  is the largest integer with  $1 + \mu + \mu^2 < C_D$

- A square block of size  $(\sqrt{p}\mu)^2$  of C is loaded in the shared cache and, subblocks of size  $\mu^2$  are distributed to every cores

- Then, repeatedly, z times:

- a row of  $\sqrt{p}\mu$  elements of B is loaded in the shared cache and distributed

- $\sqrt{p}$  elements of A are sequentially read  $\mu$  times in shared cache and distributed in order to contribute to current sub-blocks of C

### Minimizing the number of distributed-cache misses

#### Shared-cache misses

- Elements of C are loaded once in shared cache

- For each block of size  $(\sqrt{p}\mu)^2$  of C, we load:

- z rows of size  $\sqrt{p}\mu$  of B

- $z \times \sqrt{p}\mu$  elements of A.

- $M_S = mn + 2mnz/\sqrt{p}\mu$

- For large matrices, CCR is  $2/\sqrt{p}\mu$

#### Distributed-cache misses

- mn/p elements of C are loaded once in each distributed cache

- Then, at each step, we load z times:

- A row of  $\mu$  elements of B

- μ sequential elements of A

- $\bullet$   $M_D = mn/p + 2mnz/p\mu$

- For large matrices CCR is  $2/\mu$   $\odot$

- Problem statement

- Modeling multicore architectures

- Studied case and objectives

- Lower bound on communication

- 2 Maximum re-use algorithm for multicore architectures

- Minimizing the number of shared-cache misses

- Minimizing the number of distributed-cache misses

- Minimizing data access time

- Experimental results

- 3 Conclusion

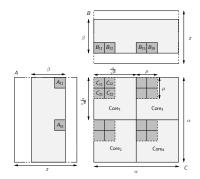

#### Why do we need a tradeoff?

- Previous objectives were antagonistic

- Bandwidths not taken into account.

$$T_{\text{data}} = \frac{M_S}{\sigma_S} + \frac{M_D}{\sigma_D}$$

#### Why do we need a tradeoff?

- Previous objectives were antagonistic

- Bandwidths not taken into account.

New objective: overall time spent in data movement

$$T_{\rm data} = \frac{M_S}{\sigma_S} + \frac{M_D}{\sigma_D}$$

#### Why do we need a tradeoff?

- Previous objectives were antagonistic

- Bandwidths not taken into account.

New objective: overall time spent in data movement

$$T_{\mathsf{data}} = \frac{M_S}{\sigma_S} + \frac{M_D}{\sigma_D}$$

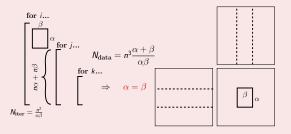

- We load in shared cache:

- a square block of size  $\alpha^2$  of C

- a block column of size  $\alpha \times \beta$  of A

- a block row of the same size of B

- $\mu^2$  blocks of C are distributed, with proper rows of B and

23/32

Complexity

- We load in shared cache:

- a square block of size  $\alpha^2$  of C

- a block column of size  $\alpha \times \beta$  of A

- a block row of the same size of B

- $\Rightarrow$  only  $z/\beta$  iterations

- $\mu^2$  blocks of C are distributed, with proper rows of B and element of A

Complexity

- We load in shared cache:

- a square block of size  $\alpha^2$  of C

- a block column of size  $\alpha \times \beta$  of A

- a block row of the same size of B

- $\Rightarrow$  only  $z/\beta$  iterations

- $\mu^2$  blocks of C are distributed, with proper rows of B and element of A

- Depending on  $\beta$ , we cannot load as many elements of C as before

- ullet We need to find the best tradeoff between eta and lpha

Problem statement

- Depending on  $\beta$ , we cannot load as many elements of C as before

- ullet We need to find the best tradeoff between eta and lpha

- New constraint on shared cache:  $2\beta\alpha + \alpha^2 \le C_S$

- Our new tradeoff algorithm has an overall data access time:

$$T_{\mathsf{data}} = \frac{mn + \frac{2mnz}{\alpha}}{\sigma_{\mathcal{S}}} + \frac{\frac{mnz}{p\beta} + \frac{2mnz}{p\mu}}{\sigma_{\mathcal{D}}}$$

The objective function is:

$$F(\alpha) = \frac{2}{\sigma_S \alpha} + \frac{2\alpha}{p\sigma_D(C_S - \alpha^2)}$$

We can now compute the best numerical values of parameters  $\alpha$  and  $\beta$

- New constraint on shared cache:  $2\beta\alpha + \alpha^2 \leq C_S$

- Our new tradeoff algorithm has an overall data access time:

$$T_{\mathsf{data}} = \frac{mn + \frac{2mnz}{\alpha}}{\sigma_{\mathcal{S}}} + \frac{\frac{mnz}{p\beta} + \frac{2mnz}{p\mu}}{\sigma_{\mathcal{D}}}$$

The objective function is:

$$F(\alpha) = \frac{2}{\sigma_S \alpha} + \frac{2\alpha}{p\sigma_D(C_S - \alpha^2)}$$

We can now compute the best numerical values of parameters  $\alpha$  and  $\beta$

#### • $\alpha$ depends on the values of bandwidths $\sigma_S$ and $\sigma_D$ .

- - When  $\sigma_D \gg \sigma_S$ :

- - On the contrary, when  $\sigma_S \gg \sigma_D$  (not realistic):

- $\alpha$  depends on the values of bandwidths  $\sigma_S$  and  $\sigma_D$ .

- ⇒ In both extreme cases, the algorithm will follow the sketch of either shared or distributed cache optimized version:

- When  $\sigma_D \gg \sigma_S$ :

- ⇒ Shared version

- On the contrary, when  $\sigma_S \gg \sigma_D$  (not realistic):

- ⇒ Distributed version

- $\alpha$  depends on the values of bandwidths  $\sigma_S$  and  $\sigma_D$ .

- ⇒ In both extreme cases, the algorithm will follow the sketch of either shared or distributed cache optimized version:

- When  $\sigma_D \gg \sigma_S$ :

- - On the contrary, when  $\sigma_S \gg \sigma_D$  (not realistic):

- $\alpha$  depends on the values of bandwidths  $\sigma_S$  and  $\sigma_D$ .

- ⇒ In both extreme cases, the algorithm will follow the sketch of either shared or distributed cache optimized version:

- When  $\sigma_D \gg \sigma_S$ :

- ⇒ Shared version.

- On the contrary, when  $\sigma_S \gg \sigma_D$  (not realistic):

- ⇒ Distributed version

Problem statement

- $\alpha$  depends on the values of bandwidths  $\sigma_S$  and  $\sigma_D$ .

- ⇒ In both extreme cases, the algorithm will follow the sketch of either shared or distributed cache optimized version:

- When  $\sigma_D \gg \sigma_S$ :

- ⇒ Shared version.

- On the contrary, when  $\sigma_S \gg \sigma_D$  (not realistic):

- $\alpha$  depends on the values of bandwidths  $\sigma_S$  and  $\sigma_D$ .

- ⇒ In both extreme cases, the algorithm will follow the sketch of either shared or distributed cache optimized version:

- When  $\sigma_D \gg \sigma_S$ :

- ⇒ Shared version.

- On the contrary, when  $\sigma_S \gg \sigma_D$  (not realistic):

- Distributed version.

#### Outline

- Problem statement

- Modeling multicore architectures

- Studied case and objectives

- Lower bound on communication

- 2 Maximum re-use algorithm for multicore architectures

- Minimizing the number of shared-cache misses

- Minimizing the number of distributed-cache misses

- Minimizing data access time

- Experimental results

- 3 Conclusion

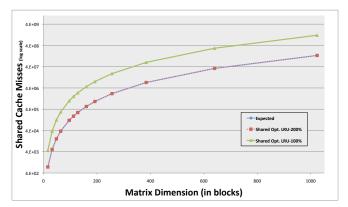

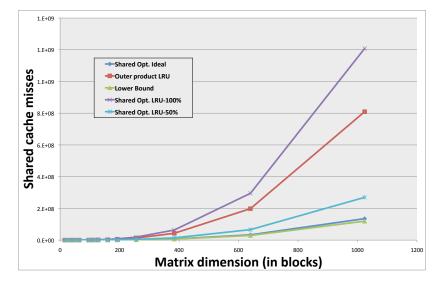

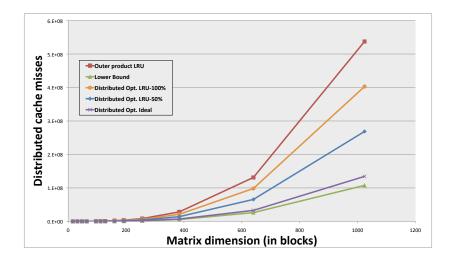

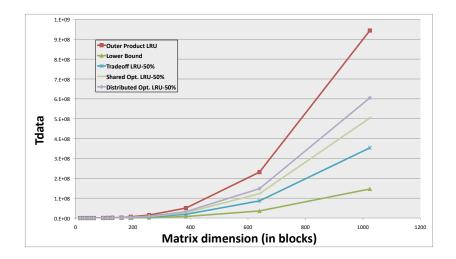

#### Replacement policy:

- Model: Caches use an ideal data replacement policy

- On most current hardware platforms: **LRU data** replacement policy

#### Replacement policy:

- Model: Caches use an ideal data replacement policy

- On most current hardware platforms: LRU data replacement policy

LRU vs. Ideal: In Cache Oblivious Algorithms, the authors stated that the number of cache misses obtained using an ideal data replacement policy on a cache of size M could be obtained using a LRU policy on a cache of size 2M

Problem statement

LRU vs. Ideal: In Cache Oblivious Algorithms, the authors stated that the number of cache misses obtained using an ideal data replacement policy on a cache of size M could be obtained using a LRU policy on a cache of size 2M

#### Benchmarked algorithms:

- Outer Product

- Multicore Maximum Re-use Algorithm:

- 3 versions:

```

Shared Opt.

Distributed Opt.

Tradeoff

```

3 simulation settings:

```

IDEAL: explicit loads in every cache, no propagation LRU-100%: LRU policy, using entire cache LRU-50%: LRU policy, half-cache for automatic prefetching

```

#### Experimental results obtained on our cache simulator

#### Experimental results obtained on our cache simulator

### Experimental results obtained on our cache simulator

#### Outline

- Problem statement

- Modeling multicore architectures

- Studied case and objectives

- Lower bound on communication

- Maximum re-use algorithm for multicore architectures

- Minimizing the number of shared-cache misses

- Minimizing the number of distributed-cache misses

- Minimizing data access time

- Experimental results

- 3 Conclusion

Complexity

### Complexity analysis of matrix product

- Model for multicore memory layout.

- For large matrices, our cache aware algorithms are close to the lower bounds.

- New algorithm realizing a tradeoff between both cache misses types.

- Our three algorithms were implemented, simulated and their behavior validated.

We now plan to extend our work to more complex kernels, like LU factorization

© Promising algorithmic research directions to explore !